FPGA Design Training Module Software, documentation and related materials:

Copyright © 2006 Altium Limited.

All rights reserved. You are permitted to print this document provided that (1) the use of such is for personal use only and will not be copied or posted on any network computer or broadcast in any media, and (2) no modifications of the document is made. Unauthorized duplication, in whole or part, of this document by any means, mechanical or electronic, including translation into another language, except for brief excerpts in published reviews, is prohibited without the express written permission of Altium Limited. Unauthorized duplication of this work may also be prohibited by local statute. Violators may be subject to both criminal and civil penalties, including fines and/or imprisonment.

Altium, Altium Designer, Board Insight, CAMtastic, CircuitStudio, Design Explorer, DXP, LiveDesign, NanoBoard, NanoTalk, Nexar, nVisage, P-CAD, Protel, SimCode, Situs, TASKING, and Topological Autorouting and their respective logos are trademarks or registered trademarks of Altium Limited or its subsidiaries.

Microsoft, Microsoft Windows and Microsoft Access are registered trademarks of Microsoft Corporation. OrCAD, OrCAD Capture, OrCAD Layout and SPECCTRA are registered trademarks of Cadence Design Systems Inc. AutoCAD is a registered trademark of AutoDesk Inc. HP-GL is a registered trademark of Hewlett Packard Corporation. PostScript is a registered trademark of Adobe Systems, Inc. All other registered or unregistered trademarks referenced herein are the property of their respective owners and no trademark rights to the same are claimed.

Module 5

i

#### FPGA Design Training Module

| 1 | FPGA   | Design                                                   | 5-1  |

|---|--------|----------------------------------------------------------|------|

|   | 1.1    | Learning Objectives                                      | 5-1  |

|   | 1.2    | Topic Outline                                            | 5-1  |

| 2 | Introd | luction to FPGA Design                                   | 5-2  |

| - | 2.1    | FPGAwhats???                                             |      |

| _ |        |                                                          |      |

| 3 |        | ing an FPGA project                                      |      |

|   | 3.1    |                                                          |      |

|   | 3.2    | A quick word about projects and design workspaces        |      |

|   | 3.3    | FPGA project                                             | 5-4  |

| 4 | FPGA   | schematic connectivity                                   | 5-5  |

|   | 4.1    | Overview                                                 | 5-5  |

|   | 4.2    | Wiring the design                                        | 5-5  |

|   | 4.3    | Including VHDL in a schematic                            |      |

|   | 4.4    | Establishing connectivity between documents              |      |

|   | 4.5    | Using buses and bus joiners                              | 5-6  |

| 5 | FPGA   | ready schematic components                               | 5-9  |

| - | 5.1    | Overview                                                 |      |

|   | 5.2    | Processor cores                                          | 5-9  |

|   | 5.3    | NanoBoard port plugins                                   | 5-10 |

|   | 5.4    | Peripheral Components                                    | 5-12 |

|   | 5.5    | Generic components                                       | 5-14 |

|   | 5.6    | Vendor macro and primitive libraries                     |      |

|   | 5.7    | Exercise 1 – Create a PWM.                               | 5-14 |

| 6 | Targe  | ting the design                                          | 5-16 |

| - | 6.1    | Constraint files                                         |      |

|   | 6.2    | Creating a new constraint file                           |      |

|   | 6.3    | Editing a constraint file                                |      |

|   | 6.4    | NanoBoard constraint files                               |      |

|   | 6.5    | Configurations                                           | 5-18 |

|   | 6.6    | Configuration Manager                                    | 5-19 |

|   | 6.7    | Exercise 2 – Configuring MyPWM                           | 5-20 |

| 7 | Runn   | ing the design                                           | 5-22 |

| ' | 7.1    | Overview                                                 | -    |

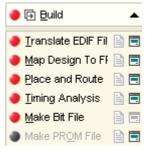

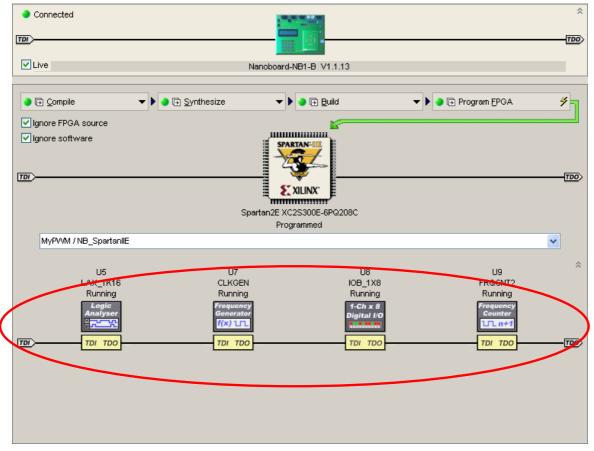

|   | 7.2    | Controlling the build process                            |      |

|   | 7.3    | Understanding the build process                          |      |

|   | 7.4    | Button regions                                           |      |

|   | 7.5    | Accessing stage reports / outputs                        |      |

|   | 7.6    | Build stages                                             |      |

|   | 7.7    | Configuring a build stage                                |      |

|   | 7.8    | How Altium Designer interacts with back-end vendor tools |      |

|   | 7.9    | Exercise 3 – Run MyPWM on the NanoBoard                  |      |

| 8 | Embo   | dded instruments                                         | 5,20 |

| U | 8.1    | Overview                                                 |      |

|   | 8.2    | On-Chip debugging                                        |      |

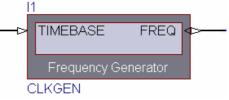

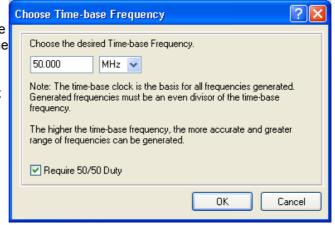

|   | 8.3    | CLKGEN                                                   |      |

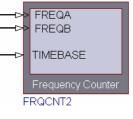

|   | 8.4    | FRQCNT2                                                  |      |

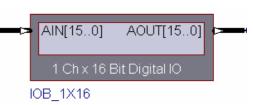

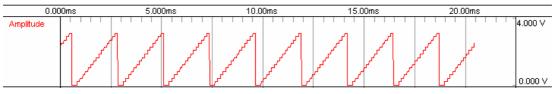

|   | 8.5    | IOB_x                                                    |      |

|   | 8.6    | LAX_x                                                    |      |

|   | -      | —                                                        |      |

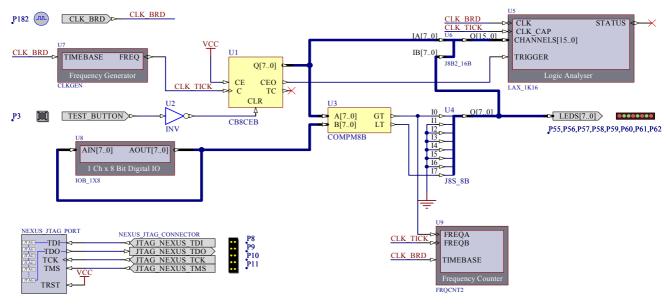

|    | 8.7     | Exercise 4 – Using embedded instruments            | 5-33 |

|----|---------|----------------------------------------------------|------|

|    | 8.8     | Where are the Instruments?                         | 5-36 |

|    | 8.9     | Enabling embedded instruments                      | 5-37 |

| 9  | Interac | cting with the NanoBoard                           | 5-38 |

|    | 9.1     | Overview                                           |      |

|    | 9.2     | NanoBoard communications                           | 5-38 |

|    | 9.3     | Technical background                               | 5-39 |

|    | 9.4     | The NanoBoard controller                           | 5-41 |

|    | 9.5     | FPGA I/O view                                      | 5-42 |

|    | 9.6     | Live cross probing                                 | 5-42 |

|    | 9.7     | Exercise 5 – View MyPWM on the NanoBoard           | 5-42 |

| 10 | Creati  | ng a core component                                | 5-43 |

|    | 10.1    | Core project                                       |      |

|    | 10.2    | Creating a core component from an FPGA project.    |      |

|    | 10.3    | A word about EDIF                                  |      |

|    | 10.4    | Setting up the core project                        | 5-44 |

|    | 10.5    | Constrain / configure                              |      |

|    | 10.6    | Creating a new constraint file.                    |      |

|    | 10.7    | Creating a configuration                           |      |

|    | 10.8    | Synthesize                                         |      |

|    | 10.9    | Publish                                            |      |

|    | 10.10   | Creating a core schematic symbol                   |      |

|    | 10.11   | Using a core component                             |      |

|    | 10.12   | Exercise 6 – Create a core component from MyPWM    |      |

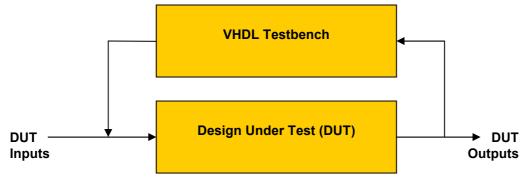

| 11 | FPGA    | design simulation                                  |      |

|    | 11.1    | Creating a testbench                               |      |

|    | 11.2    | Assigning the Testbench Document                   |      |

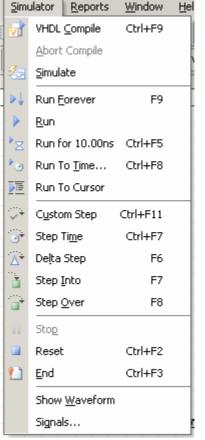

|    | 11.3    | Initiating a simulation session                    |      |

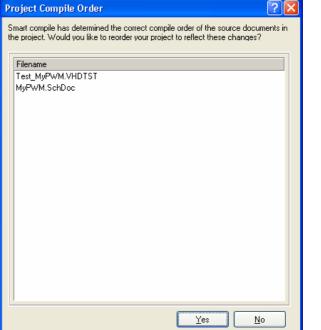

|    | 11.4    | Project compile order                              |      |

|    | 11.5    | Setting up the simulation display                  |      |

|    | 11.6    | Running and Debugging a Simulation                 |      |

|    | 11.7    | Exercise 7 – Create a testbench and simulate MyPWM | 5-58 |

| 12 | Review  | N                                                  | 5-59 |

## 1 FPGA Design

The primary objective of this day of training is to make participants proficient in the process of developing, downloading and running an FPGA design on the NanoBoard. We will go through the FPGA design framework and demonstrate just how simple FPGA design is with Altium Designer.

## 1.1 Learning Objectives

- To be competent in developing FPGA designs using standard FPGA-based libraries and the schematic capture environment

- To understand and be able to make use of the FPGA build process

- To be familiar with the peripheral capabilities of the NanoBoard and know how to incorporate their use in custom FPGA designs.

- To appreciate the different communication mechanisms used by the software to control and probe a running FPGA design.

- To be competent with the use of virtual instruments in an FPGA design.

## 1.2 Topic Outline

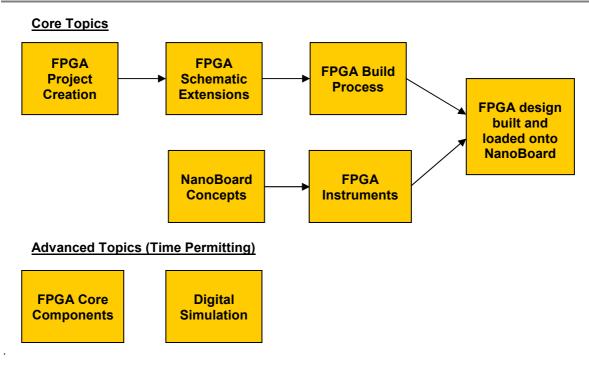

Figure 1. Topic Outline for the FPGA Design training day.

## **2** Introduction to FPGA Design

### 2.1 FPGAwhats???

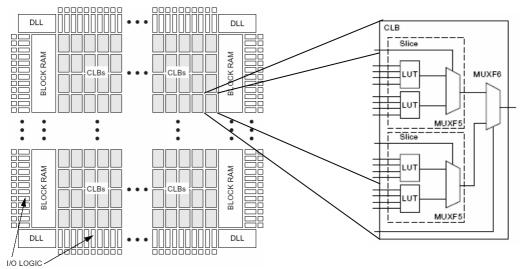

FPGA: Field Programmable Gate Array. Conceptually it can be considered as an array of Configurable Logic Blocks (CLBs) that can be connected together through a vast interconnection matrix to form complex digital circuits.

Figure 2. Exploded view of a typical FPGA

FPGAs have traditionally found use in high-speed custom digital applications where designs tend to be more constrained by performance rather than cost. The explosion of integration and reduction in price has led to the more recent widespread use of FPGAs in common embedded applications. FPGAs, along with their non-volatile cousins CPLDs (Complex Programmable Logic Devices), are emerging as the next digital revolution that will bring about change in much the same way that microprocessors did.

With current high-end devices exceeding 1000 pins and topping 1 billion transistors, the complexity of these devices is such that it would be impossible to program them without the assistance of high-level design tools. Altera and Xilinx both offer high-end EDA tool suites designed specifically to support their own devices however they also offer free versions aimed at supporting the bulk of FPGA development. Both Altera and Xilinx understand the importance of tool availability to increased silicon sales and they both seem committed to supporting a free version of their tools for some time to come.

Through the use of EDA tools, developers can design their custom digital circuits using either schematic based techniques, VHDL or a mixture of both. Prior to the Altium Designer system, vendor independent FPGA development tools were extremely expensive. Furthermore they were only useful for circuits that resided within the FPGA device. Once the design was extended to include a PCB and ancillary circuits, a separate EDA tool was needed. Altium Designer has changed all of this by being the first EDA tool capable of offering complete schematic to PCB tool integration along with multi-vendor FPGA support.

Altium made the logical extrapolation of recent trends in the FPGA world and recognized that FPGAs are no longer just for high-end designs. By making available a number of processor cores that can be downloaded onto an FPGA device and bundling them with a complete suite of embedded software development tools, Altium Designer represents a unified PCB and embedded systems development tool. FPGAs are here to stay and Altium Designer ensures that you can make the leap to the new world of digital integration with minimal pain.

## **3 Creating an FPGA project**

## 3.1 Overview

All components that will be combined together into a single FPGA design must be encapsulated within an FPGA Project.

The term "Project" refers to a group of documents that combine together to form a single target. Care must be exercised when creating a project to ensure that the correct project type is selected for the desired target.

## 3.2 A quick word about projects and design workspaces

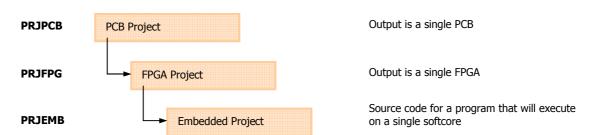

To the uninitiated, Altium Designer projects can appear a little confusing; especially when projects contain other projects. The important thing to remember is that each project can only have one output. If you have a design that requires several PCBs then you will need a separate PCB project for each PCB. If you have a design that uses several FPGAs then you will also need a separate FPGA project for each FPGA used on the final design.

Projects that are related together in some way can be grouped together using a type of 'super project' called a **Design Workspace**. Design Workspaces are simply a convenient way of packaging one or more projects together so that all projects from a single design can be opened together.

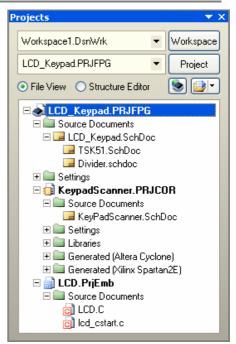

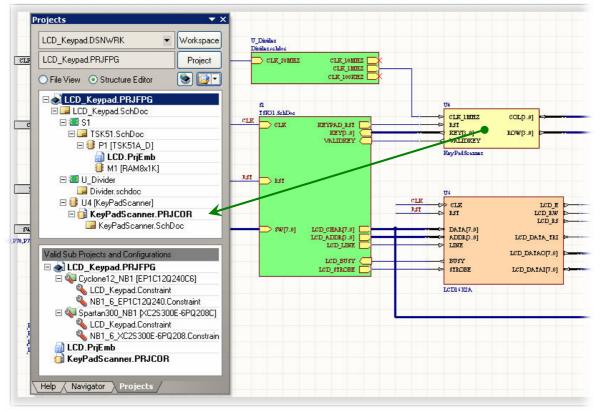

Altium Designer supports a fully hierarchical design approach. As such it is possible for some projects to contain other projects within them. Figure 3 shows a structural view of the LCD\_Keypad design that is distributed as an example in the Altium Designer installation. From this view we can observe the hierarchy of the different projects involved. The top-level project is an FPGA project called LCD\_Keypad and has the filename extension PRJFPG. Within this FPGA design is an instance of the TSK51 embedded softcore. The program or software that this embedded softcore executes is contained

Figure 3. An example of project hierarchy.

within another project called LCD.PrjEmb. Furthermore the LCD\_Keypad FPGA project also makes use of a core component called KeyPadScanner which has been defined as a core project (extension .PRJCOR).

The hierarchy of projects is given below.

Figure 4. Possible Project Hierarchy for a design containing multiple projects

A PCB Project may contain one or more FPGA projects but never the other way around. If you think about it you will recognize that it is quite intuitive; a PCB contains FPGAs whereas an FPGA can't contain a PCB. Similarly, an FPGA could contain one or more custom FPGA cores or

microprocessor softcores. A unique Core Project will define each FPGA core component and a unique Embedded Project will define the software that executes on each of the softcores.

## 3.3 FPGA project

An FPGA project should be used when the target is a single FPGA. The output of an FPGA project will be a configuration bit file that can be used to program an FPGA.

The simplest way to create a project is from the File menu (File » New » Project).

| DXP   | Eile | <u>Edit View Project T</u> oo          | ls | Debu     | ıg <u>W</u> indow <u>H</u> el | lp        | _          |                       |     |

|-------|------|----------------------------------------|----|----------|-------------------------------|-----------|------------|-----------------------|-----|

| I 🗅 📂 |      | New                                    | ►  |          | <u>S</u> chematic             |           | -          |                       | 1 🗉 |

|       | 2    | Open Ctrl+O                            |    | 矙        | <u>Р</u> СВ                   |           | -          |                       |     |

|       |      | <u>⊂</u> lose Ctrl+F4                  |    | (V)      | <u>V</u> HDL Document         |           |            |                       |     |

|       | 12   | Open Project                           |    | Ø        | Verilog Document              |           |            |                       |     |

|       |      | Open Design Wor <u>k</u> space         |    | C        | $\subseteq$ Source Documer    | nt        |            |                       |     |

|       |      | Save Ctrl+S                            |    | ы        | C <u>H</u> eader Docume       | ent       |            |                       |     |

|       |      | Save <u>A</u> s                        | ĺ  | A        | ASM Source Docur              | ment      |            |                       |     |

|       |      | –<br>Save Copy As…                     |    |          | <u>T</u> ext Document         |           |            |                       |     |

|       |      | Save All                               | ĺ  | <b>æ</b> | CA <u>M</u> Document          |           |            |                       |     |

|       |      | Save Project As                        |    | <u> </u> | Outp <u>u</u> t Job File      |           |            |                       |     |

|       |      | Save Design Workspace As               |    | ٥,       | Database Lin <u>k</u> File    | •         |            |                       |     |

|       |      |                                        |    |          | Project                       | •         | <b>1</b>   | PC <u>B</u> Project   |     |

|       |      | Page Setup                             |    |          | Library                       | •         | ۲          | EPGA Project          |     |

|       |      | Print Pre <u>v</u> iew<br>Print Ctrl+P | ĺ  |          | Script Files                  | +         | <b>i</b>   | Co <u>r</u> e Project |     |

|       | 3    |                                        |    |          | Mi <u>x</u> ed-Signal Simul   | Ilation 🕨 | 5          | Integrated Librar     | у   |

|       |      | Protel 99 SE Import Wizard             |    |          | <u>O</u> ther                 | •         | <b>a</b> ) | Embedded Projec       | t   |

|       |      | Recent Documents                       | •  | <b>a</b> | Design <u>W</u> orkspace      | e         | ടി         | Script Project        |     |

|       |      | Recent Projects                        |    |          |                               |           |            |                       |     |

|       |      | Recent Design Workspaces               | ×  |          |                               |           |            |                       |     |

|       |      | E <u>×</u> it Alt+F4                   |    |          |                               |           |            |                       |     |

Figure 5. Creating a new FPGA project

## **4 FPGA schematic connectivity**

## 4.1 Overview

Schematic documents used in FPGA designs are converted to VHDL in the process of being compiled into the design. This process is totally transparent to the user and does not require the user to know anything specific about VHDL. However the VHDL conversion process does place some requirements onto the schematic document that must be considered to ensure that the conversion process goes smoothly and that the resultant VHDL is valid.

In this section we will discuss some of the extensions that have been added to the schematic environment for the purposes of servicing FPGA designs.

## 4.2 Wiring the design

Connectivity between the component pins is created by physical connectivity, or logical connectivity. Placing wires that connect component pins to each other creates *physical* connectivity. Placing matching net identifiers such as net labels, power ports, ports and sheet entries creates *logical* connectivity. When the design is compiled the connectivity is established, according to the net identifier scope defined for the project.

Note that while the environment supports compiling projects using either a flat or hierarchical

⚠

# connective structure, FPGA projects must be hierarchical. **4.3** Including VHDL in a schematic

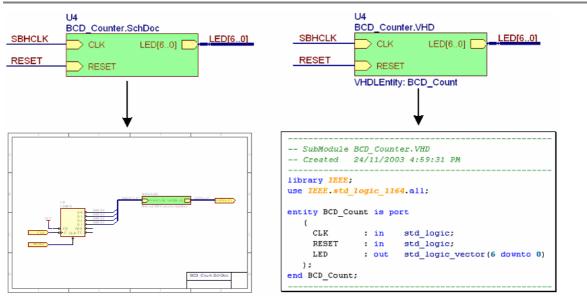

Figure 6. Linking schematic sheet symbols to lower level documents

VHDL sub-documents are referenced in the same way as schematic sub-sheets, by specifying the sub-document filename in the sheet symbol that represents it. The connectivity is from the sheet symbol to an entity declaration in the VHDL file. To reference an entity with a name that is different from the VHDL filename, include the VHDLEntity parameter in the sheet symbol whose value is the name of the Entity declared in the VHDL file (as shown above).

## 4.4 Establishing connectivity between documents

Hierarchical net and bus connectivity between documents obeys the standard hierarchical project connection behavior, where ports on the sub-document connect to sheet entries of the same name in the sheet symbol that represents that document, as shown below.

Figure 7. Connectivity between sheet symbols and lower level documents

## 4.5 Using buses and bus joiners

Typically there are a large number of related nets in a digital design. Buses can play an important role in managing these nets, and help present the design in a more readable form.

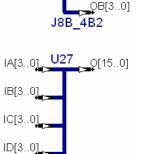

Buses can be re-ordered, renamed, split, and merged. To manage the mapping of nets in buses, there is a special class of component, known as a bus joiner. Bus joiners can be placed from the FPGA

Generic.IntLib library (bus joiner names all start with the letter J). Figure 8 shows examples of using bus joiners. There are also many examples of using bus joiners in the example designs in the software.

| PORTA[70] [[70] U29 |        | LCD_STROBE<br>LCD_LINE<br>LCD_RST<br>KEYPAD_RST | LCD_STROBE<br>LCD_LINE<br>LCD_RST<br>KEYPAD_RST |

|---------------------|--------|-------------------------------------------------|-------------------------------------------------|

| DOORS[30]           | IA[30] | U27 <u>0[150]</u>                               | INPUTS[150]                                     |

|                     | IB[30] |                                                 |                                                 |

| WINDOWS[30]         | IC[30] |                                                 |                                                 |

| SMOKE[30]           | ID[30] | J4B4 16B                                        |                                                 |

Figure 8. Examples of using bus joiners

Note that apart from the JB-type joiner, all bus joiner pins have an IO direction – use the correct joiner to maintain the IO flow. Pin IO can be displayed on sheet, enable the **Pin Direction** option in the schematic **Preferences** dialog.

The use of bus joiners in FPGA designs is a significant departure from how bus connectivity is established on other schematic documents however the benefits of bus joiners soon become clear. Nets extracted from a bus joiner need not be related in any way – ie. have the same name and differing only by number (Data[0], Data[1], Data[2], ... etc). The bus joiner example above shows how a single bus can be used to route a number of LCD and Keypad signals together. Previously this was not possible in a bus.

#### 4.5.1 Bus joiner naming convention

Bus joiners follow a standardized naming convention so that they can be easily found within the FPGA Generic.IntLib library.

J<width><B/S>[Multiples]\_<width><[B/S]>[Multiples]

For example:

J8S\_8B: describes a bus joiner that routes 8 single wires to a single, 8-bit bus.

J8B\_8S: describes a bus joiner that routes a single, 8-bit bus into 8 single wires.

J8B\_4B2: describes a bus joiner that routes a single 8-bit bus into two 4-bit busses,

J4B4\_16B: describes a bus joiner that routes four, 4-bit busses into a single 16-bit bus.

OA[3..0]

#### 4.5.2 Bus joiner splitting / merging behaviour

The basic rule is that bus joiners separate/merge the bits (or bus slice) from least significant bit (or slice) down to most significant bit (or slice).

For example, in Figure 12 U17 splits the incoming 8-bit bus on pin I[7..0] into two 4-bit bus slices, OA[3..0] and OB[3..0]. Obeying the least to most mapping at the slice level, the lower four bits of the input bus map to OA[3..0], and the upper four bits map to OB[3..0]. Following this through to the bit level, I0 will connect to OA0, and I7 will connect to OB3.

The joiner U27 merges the four incoming 4-bit slices into a 16-bit bus. With this joiner IA0 connects to O0, and ID3 connects to O15.

#### 4.5.3 Matching buses of different widths using the JB-type bus joiner

J4B4\_16B

U17

1[7..0]

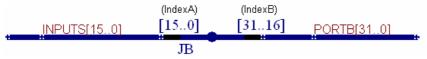

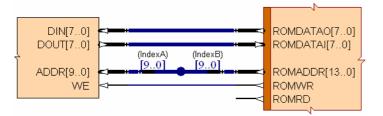

The JB-type bus joiner allows you to match nets in buses of different widths. It does this via 2 component parameters, IndexA and IndexB that map from one bus through to the other bus. These indices must be defined when you use a JB joiner.

Figure 10. Join buses of different widths, and control the net-to-net mapping

Read the flow of nets through a JB-type bus joiner by matching from the nets in the attached bus, to the first index on the bus joiner, to the second index in the bus joiner, to the nets defined in the second bus net label.

Left Bus  $\leftrightarrow$  IndexA  $\leftrightarrow$  IndexB  $\leftrightarrow$  Right Bus

The rules for matching nets at each of the  $\leftrightarrow$  points are as follows:

Figure 11. An example of using the JB bus joiner to achieve sub-set mapping

If both bus ranges are descending, match by same bus index (one range must lie within the other for valid connections). In Figure 11 the matching is:

ADDR9  $\leftrightarrow$  IndexA9  $\leftrightarrow$  IndexB9  $\leftrightarrow$  ROMADDR9, thru to

$\texttt{ADDR0} \iff \texttt{IndexA0} \iff \texttt{IndexB0} \iff \texttt{ROMADDR0}$

(In this example ROMADDR10 thru ROMADDR13 will be unconnected)

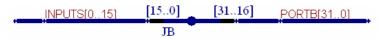

[15..0] [31..16]INPUTS[15..0] PORTB[31..0] ЛВ

Figure 12. Using of a bus joiner for offset mapping

In Figure 12 the matching is:

INPUTS15  $\leftrightarrow$  IndexA15  $\leftrightarrow$  IndexB31  $\leftrightarrow$  PORTB31, thru to

```

INPUTS0 \leftrightarrow IndexA0 \leftrightarrow IndexB0 \leftrightarrow PORTB16

```

The document is for study only if tort to your rights, please inform us, we will delete

Figure 9. Bus joiners merge and split buses

Figure 13. Using a bus joiner for range inversion

• If one bus range is descending and another is ascending, the indices are matched from left to right. In Figure 13 the matching is:

INPUTS0  $\leftrightarrow$  IndexA15  $\leftrightarrow$  IndexB31  $\leftrightarrow$  PORTB31, thru to

$INPUTS15 \leftrightarrow IndexA0 \leftrightarrow IndexB16 \leftrightarrow PORTB16$

| INPUTS[150] | [150] | [3116] | PORTB[031] |

|-------------|-------|--------|------------|

|             | JB    |        |            |

Figure 14. Another example of using a bus joiner for range inversion

• In Figure 14 the matching is:

•

<code>INPUTS15</code>  $\leftrightarrow$  <code>IndexA15</code>  $\leftrightarrow$  <code>IndexB31</code>  $\leftrightarrow$  <code>PORTB0</code>, thru to

$\mathsf{INPUTS0} \leftrightarrow \mathsf{IndexA0} \leftrightarrow \mathsf{IndexB16} \leftrightarrow \mathsf{PORTB15}$

## **5 FPGA ready schematic components**

### 5.1 Overview

A wide variety of FPGA-ready schematic components are included with the system, ranging from processors, to peripheral components, down to generic logic. Placing and wiring these schematic components, or writing VHDL, captures the hardware design. The FPGA-ready schematic components are like traditional PCB-ready components, except instead of the symbol being linked to a PCB footprint each is linked to a presynthesized EDIF model.

As well as components that you use to implement your design, the available FPGA libraries include components for the virtual instruments, and the components that are mounted on the NanoBoard and are accessible via the pins on the FPGA. The role of each type of component is described below.

Help for all FPGA-ready components can be accessed by pressing the F1 key whilst the component is selected in the library list.

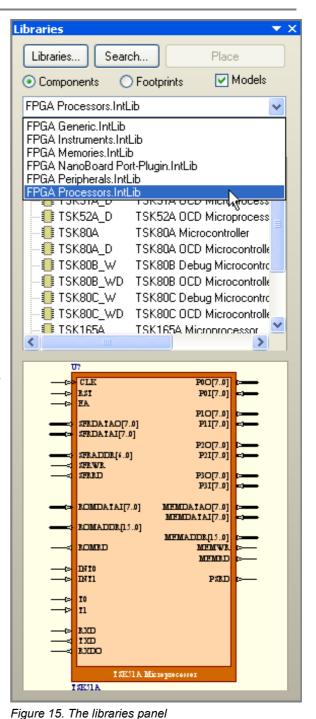

## 5.2 Processor cores

Softcore processors can be placed from the \Program Files\Altium Designer 6\Library\Fpga\FPGA Processors.IntLib library. At the time of release of this manual, the following processors and related embedded software tools are supported:

- TSK165 Microchip 165x family instruction set compatible MCU

- TSK51/52 8051 instruction set compatible MCU

- TSK80 Z80 instruction set compatible MCU

- PPC405A Embedded Power PC Core available on some Virtex FPGAs.

- TSK3000 32-bit RISC processor.

There is also full embedded tool support for:

- Xilinx MicroBlaze soft core, which requires the appropriate Xilinx device and license to use

- Xilinx Virtex-2 Pro based PowerPC 405

- AMCC PowerPC 405 discrete processor family

- ARM7, ARM9, ARM9E & ARM10E families, supported in the Sharp BlueStreak (ARM20T) discrete processor family

## 5.3 NanoBoard port plugins

Hardware resources on the NanoBoard can be accessed via the use of components from the \Program Files\Altium Designer 6\Library\Fpga\FPGA NanoBoard Port-Plugin.IntLib library. A summary of the components is given below:

| NanoBoard Port-Plugin.Int                      | Lib                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Name in Library                                | Description                                                                                                                                                                                                                                                                                                                                           | Symbol                                                                                                       |

| ADCDAC_I2C                                     | The MAX1037 ADC converter<br>provides four multiplexed analogue<br>inputs selectable by application<br>software via the I2C connection.                                                                                                                                                                                                               | SDA<br>SCL                                                                                                   |

| AUDIO_DAC                                      | The NanoBoard provides and SPI-<br>based 8-bit audio codec, together<br>with relevant analogue pre and post<br>conditioning circuitry (Maxim part<br>number MAX1104).                                                                                                                                                                                 | -> AUDIO DIN<br>-> AUDIO DOUT<br>-> AUDIO SCLK<br>-> AUDIO SPICS                                             |

| CANCNTR                                        | The CAN Port is connected to a<br>Microchip MCP2551 CAN<br>transceiver IC.                                                                                                                                                                                                                                                                            | -> CAN TXD<br>-> CAN RXD                                                                                     |

| CLOCK_SUPPLY<br>CLOCK_BOARD<br>CLOCK_REFERENCE | An SPI-based system clock<br>generator provides a fixed 20MHz<br>clock (CLK_REF) and a user-<br>programmable clock providing<br>frequencies from 6 to 200MHz<br>(CLK_BRD).                                                                                                                                                                            | CLK BRD<br>CLK REF<br>CLK BRD<br>CLK BRD<br>CLK BRD<br>CLK REF                                               |

| DAISYIN_SLAVEIO<br>DAISYOUT_MASTERIO           | The NanoBoard can be connected in<br>a daisychain configuration, allowing<br>multiple NanoBoard applications to<br>be controlled by the software. The<br>Master and Slave I/O headers can<br>be used to provide an application-<br>defined communication resource<br>between daughterboard applications<br>on separate NanoBoards in a<br>daisychain. | DaisyIn0<br>DaisyIn1<br>DaisyIn2<br>DaisyIn2<br>DaisyUn2<br>DaisyOut0<br>DaisyOut1<br>DaisyOut2<br>DaisyOut3 |

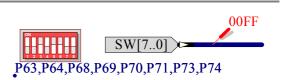

| DIPSWITCH                                      | A standard DIP switch is wired as an<br>active low device to the NanoBoard<br>daughter board.                                                                                                                                                                                                                                                         | SW[70] >                                                                                                     |

| KEYPAD                                         | The keypad array consists of 16<br>miniature pushbuttons arranged in a<br>4 x 4 matrix. The keypad is<br>organized so that a row-column<br>scanning process can read the<br>status of each key.                                                                                                                                                       | $(1) \begin{pmatrix} a \\ c \\$                                      |

| LED                                            | A set of 8 active high LEDs are<br>connected to separate pins of the<br>daughter board and can be driven by<br>a user application.                                                                                                                                                                                                                    | ►> LEDS[70] ●●●●●●●                                                                                          |

| NanoBoard Port-Plugin.Int                             |                                                                                                                                                                                                                                                          |                                                                                                         |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Name in Library                                       | Description                                                                                                                                                                                                                                              | Symbol                                                                                                  |

| MEMORY0<br>MEMORY1<br>MEMORY256KX8                    | Two 128k x 8 static RAM devices are<br>included on the NanoBoard and<br>wired directly to I/O pins on the<br>daughter board. The SRAM devices<br>have a common Chip Select and<br>Address signals but separate 8-bit<br>data bus and Read/Write signals. |                                                                                                         |

|                                                       |                                                                                                                                                                                                                                                          |                                                                                                         |

| LCD<br>LCD_MEMORY0<br>LCD_MEMORY1<br>LCD_MEMORY256KX8 | The NanoBoard contains a 16-<br>character by 2-line industry standard<br>LCD with LED backlight.                                                                                                                                                         | → LCD E<br>→ LCD RW<br>→ LCD BB[70]                                                                     |

| NEXUS_JTAG_<br>CONNECTOR                              | The Nexus, or soft devices chain, is<br>implemented in the FPGA design by<br>the inclusion of this connector.                                                                                                                                            | → JTAG NEXUS TDI<br>→ JTAG NEXUS TDO<br>→ JTAG NEXUS TCK<br>→ JTAG NEXUS TMS                            |

| PS2A<br>PS2B                                          | The NanoBoard features two PS2<br>ports – PS2A nominally may be used<br>for a keyboard and PS2B may be<br>used for a mouse.                                                                                                                              | PSZA CLK<br>PSZA DATA                                                                                   |

| RS232CNTR                                             | A standard DTE RS232 port is<br>provided with TXD, RXD, RTS and<br>CTS signals connected.                                                                                                                                                                | -> RS TX<br>-> RS RX<br>-> RS RTS<br>-> RS RTS<br>T                                                     |

| SERIALFMEMORY                                         | Two ST M25P40 low-cost 4-Mbit<br>serial flash RAM devices are<br>installed as a non-volatile memory<br>source.                                                                                                                                           | SPI DOUT<br>SPI DIN<br>SPI CLK<br>SPI CLK<br>SPI SEL ↔                                                  |

| SPEAKER                                               | The NanoBoard's magnetic audio<br>transducer can operate as a beeper<br>when driven by a square-wave signal<br>or can be pulse-width modulated to<br>produce more complex sounds.                                                                        | -> SPEAKER )                                                                                            |

| SRAM_DAUGHTER0<br>SRAM_DAUGHTER1                      | Provision has been made for<br>connection of to up to two 128k x 8<br>SRAM devices placed on a<br>NanoBoard daughter board.                                                                                                                              | SRAM0 D[15.0]<br>-> SRAM0 E<br>SRAM0 A[18.0]<br>-> SRAM0 W<br>-> SRAM0 OE<br>-> SRAM0 UB<br>-> SRAM0 LB |

| TEST_BUTTON                                           | Although this button is labeled 'Test',<br>it has no intrinsic function and can be<br>used for any purpose by the user<br>application.                                                                                                                   | TEST_BUTTON >                                                                                           |

| VGACNTR                                               | The VGA port provides a VGA<br>compatible RGB video monitor port.<br>With two-bits per color channel, the<br>VGA port is capable of representing<br>64 colors.                                                                                           | VGA R[10]           ∨GA G[10]           ∨GA B[10]           ∨GA HSYN           ∨ VGA VSYN               |

## 5.4 Peripheral Components

Many of the hardware resources present on the NanoBoard come with peripheral modules that can be included in the FPGA design to ease interfacing to the external port.

Peripherals can be placed from the \Program Files\Altium Designer 6\Library\Fpga\FPGA Peripherals.IntLib library.

| FPGA Peripherals.IntLib                           |                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                               |  |  |  |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name in Library                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                   | Symbol                                                                                                                                                                        |  |  |  |

| CAN                                               | <b>CAN Controller</b> – parallel to serial interface,<br>implementing a Controller Area Network<br>serial communications bus on the serial side.<br>The CAN serial bus provides high bit rate,<br>high noise immunity and error detection. The<br>Controller implements the BOSCH CAN 2.0B<br>Data Link Layer Protocol. The CAN controller<br>can be used in conjunction with the CAN<br>interface hardware on the NanoBoard. | U?<br>CLK DATAO[7.0]<br>RST DATAI[7.0]<br>DATAZ<br>CS<br>ENABLE ADDR[6.0]<br>WR<br>WR<br>NTT<br>AS<br>NTO<br>RXD<br>MODE TX0<br>TX1<br>TXEN<br>CLK_OUT<br>OUTCTRL[5.0]<br>CAN |  |  |  |

| EMAC<br>EMAC_MD<br>EMAC_MD_W<br>EMAC_W            | Ethernet Media Access Controller –<br>provides an 8-bit IEEE802.3 compliant<br>interface between a processor and a<br>standard Physical Layer device (PHY).                                                                                                                                                                                                                                                                   | U?<br>CLK INIT<br>DELAY[70]<br>FPGA_STARTUP8<br>U?<br>CLK INIT<br>DELAY[150]<br>FPGA_STARTUP16<br>U?<br>DELAY[310]<br>FPGA_STARTUP32                                          |  |  |  |

| FPGA_STARTUP8<br>FPGA_STARTUP16<br>FPGA_STARTUP32 | <b>FPGA Startup</b> – user-definable power-up<br>delay, used to implement power-on reset. An<br>internal counter starts on power up, counting<br>the number of clock cycles specified by the<br>Delay pin, the output pin being asserted<br>when the count is reached.                                                                                                                                                        | U?<br>CLK INIT<br>DELAY[7.0]<br>FPGA_STARTUP8<br>U?<br>CLK INIT<br>FPGA_STARTUP16<br>U?<br>DELAY[15.0]<br>FPGA_STARTUP16<br>U?<br>DELAY[1.0]<br>FPGA_STARTUP32                |  |  |  |

| I2CM                                              | <b>I2C</b> – parallel to serial interface,<br>implementing an Inter-Integrated Circuit (I2C)<br>2-wire serial bus on the serial side.<br>Controllers only support a single master I2C<br>serial bus system. The I2C controller can be<br>used in conjunction with the I2C interface<br>hardware on the NanoBoard.                                                                                                             | U?<br>CLK SDATA EN<br>RST SDATAO<br>DATAO[7.0]<br>DATAO[7.0]<br>SCLK EN<br>SCLKO<br>ADDR[2.0]<br>RD<br>INT<br>I2CM                                                            |  |  |  |

| KEYPADA                                           | <b>Keypad Controller</b> – 4 x 4 keypad scanner<br>with de-bounce. Can be used in a polled or<br>interrupt driven system. Also available in<br>either Wishbone or non-Wishbone variants.<br>The Keypad controller can be used in<br>conjunction with the keypad on the<br>NanoBoard.                                                                                                                                          | U?<br>CLK_IMHZ COL[3.0]<br>RST<br>ROW[3.0]<br>KEY[3.0]<br>VALIDKEY<br>KEYPADA                                                                                                 |  |  |  |

| LCD16X2A                                          | <b>LCD Controller</b> – easy to use controller for a 2 line by 16-character LCD module. The LCD controller can be used in conjunction with the LCD display on the NanoBoard.                                                                                                                                                                                                                                                  | U?<br>CLK LCD E<br>RST LCD RW<br>DATA[7.0]<br>ADDR[3.0] LCD DATA TRI<br>ADDR[3.0] LCD DATAO[7.0]<br>EUSY<br>STROBE<br>LCD16X2A                                                |  |  |  |

| Name in Library                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PS2                                                                                                      | <b>PS2 Controller</b> – parallel to serial interface<br>providing a bi-directional, synchronous serial<br>interface between a host MCU and a PS/2<br>device (keyboard or mouse). The PS2<br>controller can be used in conjunction with<br>either of the two sets of PS2 interface<br>hardware on the NanoBoard.                                                                                                                                                                                     | U?<br>CLK PS2CLKTRI<br>RST PS2CLKO<br>PS2CLKI<br>DATAO[7.0]<br>DATAO[7.0]<br>PS2DATATRI<br>PS2DATATRI<br>PS2DATAI<br>STROBE<br>INT<br>STROBE<br>NT<br>PS2<br>CLK_IMHZ<br>PS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SRL0                                                                                                     | <b>SRL0</b> – simple parallel to serial interface, full<br>duplex, single byte buffering. The SRL0 can<br>be used in conjunction with the RS-232<br>interface hardware on the NanoBoard.                                                                                                                                                                                                                                                                                                            | U?<br>CLK TX<br>RST RX<br>DATAI[70] RXO<br>DATAO[70]<br>ADDR[30]<br>WR<br>RD<br>INT<br>SRL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TMR3                                                                                                     | <b>TMR3</b> – dual timer unit, 16, 13 and 8-bit timer/counter modes.                                                                                                                                                                                                                                                                                                                                                                                                                                | U?<br>CLK TA<br>RST GATEA<br>DATAI[7.0]<br>DATAO[7.0] TB<br>GATEB<br>ADDR[2.0] TB_OV<br>WR<br>RD<br>INT<br>TMR3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VGA                                                                                                      | VGA – VGA controller that creates a simple<br>method of implementing a VGA interface,<br>presenting video memory as a flat address<br>space. Supports VGA and SVGA resolutions,<br>and B&W, 16 and 64 color. Outputs digital<br>RGB and H+V sync. The VGA controller can<br>be used in conjunction with the VGA output<br>on the NanoBoard.                                                                                                                                                         | U?<br>CLK HSYNC<br>RST VSYNC<br>RESOLUTION RI<br>CMOD[1.0] R0<br>DISPSIZE H[9.0] G1<br>DISPSIZE_V[9.0] G0<br>B1<br>RD B0<br>DATA[7.0]<br>ADDR_PIXEL[18.0]<br>VGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MAX1104_DAC                                                                                              | <b>DAC</b> – This digital to analogue controller<br>module provides a simple interface to the<br>MAX1104 8-bit CODEC device on the<br>NanoBoard.                                                                                                                                                                                                                                                                                                                                                    | U?<br>CLK SPI DOUT<br>RST SPI DIN<br>SPI SCLK<br>DATA[7.0] SPI_CS<br>MAX1104_DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PRTIO1X8<br>PRTIO2X8<br>PRTIO4X8<br>PRTIOX1X8<br>PRTIOX2X8<br>PRTIOX4X8<br>PRTO1X8<br>PRTO2X8<br>PRTO4X8 | <ul> <li>PRTx – The PRTx Parallel Port Unit is simply a register interface for storing data to be transferred to/from another device in a design. For example when used with a microcontroller such as the TSK80x, which does not have any on-core port interfaces, the unit provides a valuable new extension to the processor's feature set.</li> <li>PRTOx – output only port devices</li> <li>PRTIOX – I/O port devices with additional tristate buffer enable output for each port.</li> </ul> | U7         U7           GLK         PA0[7,0]           BST         PA0[7,0]           DATA[7,0]         DATA[7,0]           DATA[7,0]         PA0[7,0]           DATA[7,0] |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CK         TBSN[7:0]         CK         REST         PAO(7:0)           DATAU[7:0]         PAO[7:0]         CK         REST         PAO(7:0)           DATAU[7:0]         PAO[7:0]         DATAU[7:0]         DATAU[7:0]           ADDR         PAO[7:0]         DATAU[7:0]         REST           VI         TRENNAN         TRENT 0         TRENT 0           UT         CK         TBSN[7:0]         TRENT 0           DATAU[7:0]         PAO[7:0]         REST 0         TRENT 0           DATAU[7:0]         PAO[7:0]         PAO[7:0]         REST 0           DATAU[7:0]         PAO[7:0]         PAO[7:0]         PAO[7:0]           DATAU[7:0]         PAO[7:0]         PAO[7:0]         PAO[7:0]           ADDRIT 0         PAO[7:0]         PAO[7:0]         PAO[7:0]           ADDRIT 0         PAO[7:0]         PAO[7:0]         PAO[7:0]       |

## 5.5 Generic components

Generic components can be placed from the library \Program Files\Altium Designer 6\Library\Fpga\FPGA Generic.IntLib. This library is included to implement the interface logic in your design. It includes pin-wide and bus-wide versions for many components, simplifying the wiring complexity when working with buses. As well as a broad range of logic functions, the generic library also includes pullup and pulldown components as well as a range of bus joiners, used to manage the merging, splitting and renaming of buses.

For a definition of the naming convention used in the generic library and a complete listing of available devices, refer to the document: CR0118 FPGA Generic Library Guide.pdf.

Wild card characters can be used to filter when searching the component library.

# 5.6 Vendor macro and primitive libraries

If vendor independence is not required, there are also complete primitive and macro libraries for the currently supported vendors/device families. These libraries can be found in the respective Actel, Altera, Lattice and Xilinx sub-folders in \Program Files\Altium Designer 6\Library\. The macro and primitive library names end with the string \*FPGA.IntLib. Note that some vendors require you to use primitive and macro libraries that match the target device. Designs that include vendor components *cannot* be re-targeted to another vendor's device.

#### Libraries Place RAMD Libraries.. Search. FPGA Generic.IntLib v ... \*memory\* ¥ Component Description Library 📒 RAMD Dual Port Random Access Memo FPGA Generic.Ir 间 RAMDE Dual Port Random Access Memo FPGA Generic.Ir BAMDR Dual Port Random Access Memo FPGA Generic.In BAMDRE Dual Port Bandom Access Memo EPGA Generic In 📒 RAMS Single Port Random Access Merr FPGA Generic.Ir RAMSE Single Port Random Access Merr FPGA Generic.In RAMSR Single Port Random Access Merr FPGA Generic.In 📑 RAMSRE Single Port Random Access Merr FPGA Generic.Ir 间 ROMD Dual Port Read Only Memory FPGA Generic.Ir Dual Port Read Only Memory Wit FPGA Generic.Ir BOMDE 📑 ROMDR Dual Port Read Only Memory with FPGA Generic.In 📑 ROMDRE Dual Port Read Only Memory Wit FPGA Generic.Ir ROMS Single Port Read Only Memory FPGA Generic.Ir 📒 Romse Single Port Read Only Memory W FPGA Generic.Ir 📑 ROMSR Single Port Read Only Memory wi FPGA Generic.Ir ROMSRE Single Port Read Only Memory W FPGA Generic. Ir 1885 components CLRA [..]ARICI [..]ATUOC ADDRA[..] WEA CLEE DINB[.. DOUTB[.. ADDRB[..] WEE RAMD

Figure 16. Using wildcards to quickly find a specific component in the Generic Library

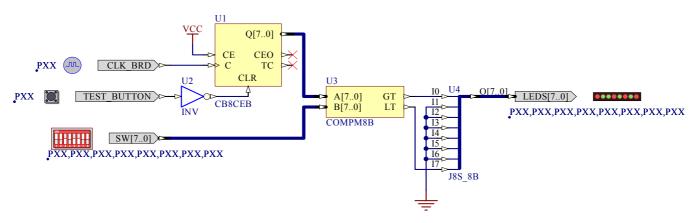

## 5.7 Exercise 1 – Create a PWM.

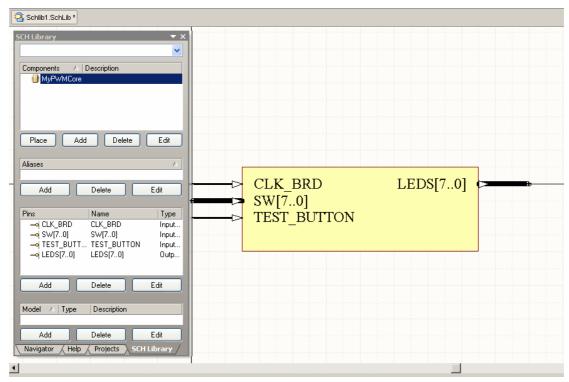

In this exercise we will create our first FPGA design. In order to complete this task you will need to use the following components from their respective libraries:

- 1. Open a new FPGA Project. Save it as MyPWM.PrjFpg

- 2. Add a new schematic to your project and save it as MyPWM.SchDoc

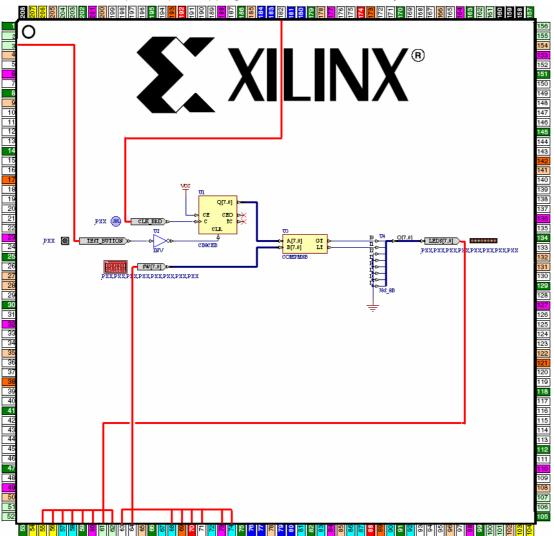

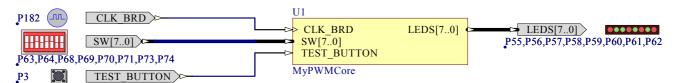

Figure 17. Place and wire the components to create the Pulse Width Modulator

### www.cadfamily.com EMail:cadserv21@hotmail.com The document is for study only,if tort to your rights,please inform us,we will delete

3. Using components from the two libraries FPGA Generic.IntLib and FPGA NanoBoard Port-Plugin.IntLib, place and wire the schematic shown in Figure 17.

| Component                                                                                                                                                                                                   | Library                           | Name in Library |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|

| PXX CLK_BRD >>-                                                                                                                                                                                             | FPGA NanoBoard Port-Plugin.IntLib | CLOCK_BOARD     |

| PXX TEST_BUTTON                                                                                                                                                                                             | FPGA NanoBoard Port-Plugin.IntLib | TEST_BUTTON     |

| SW[7.0]       PXX,PXX,PXX,PXX,PXX,PXX,PXX,PXX                                                                                                                                                               | FPGA NanoBoard Port-Plugin.IntLib | DIPSWITCH       |

| PXX,PXX,PXX,PXX,PXX,PXX,PXX,PXX,PXX                                                                                                                                                                         | FPGA NanoBoard Port-Plugin.IntLib | LED             |

| $UI$ $Q[70] \qquad \qquad$                                                           | FPGA Generic.IntLib               | CB8CEB          |

|                                                                                                                                                                                                             | FPGA Generic.IntLib               | INV             |

| $\begin{array}{c} U3 \\ \clubsuit & A[7.0] \\ B[7.0] \\ COMPM8B \end{array} \qquad $ | FPGA Generic.IntLib               | COMPM8B         |

| 10 U4 0[70]<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>J88_8B                                                                                                                                             | FPGA Generic.IntLib               | J8S_8B          |

Figure 18. Save your work – we will continue with this schematic soon

## 6 Targeting the design

The schematic that we have just created contains all of the connectivity that must occur internally on our FPGA device but we still need some further information to map the ports on the FPGA schematic to physical pins on an actual FPGA device. This process is called targeting our design.

## 6.1 Constraint files

Rather than storing device and implementation specific data such as pin allocations and electrical properties in the source VHDL or Schematic documents, this information is stored in separate files – called *Constraint files*. This decoupling of the logical definition of an FPGA design from its physical implementation allows for quick and easy re-targeting of a single design to multiple devices and PCB layouts.

Below we see a conceptual representation of an FPGA design sitting inside an FPGA device. The red lines indicate the port-to-pin mappings that would be handled by the constraint file.

Figure 19. Conceptual view showing the linkage of ports on an FPGA schematic routed to physical device pins.

## 6.2 Creating a new constraint file

A constraint file can be added to a project by right-clicking the FPGA project in the **Projects** panel and selecting **Add New to Project » Constraint File**. A shell constraint file will be created.

## 6.3 Editing a constraint file

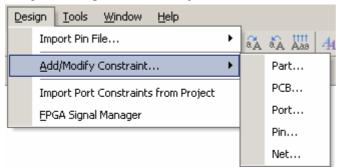

Constraint file additions / modifications can be made by manually editing the constraint file or by using the **Design** » **Add/Modify Constraint** menu.

Figure 20. Add/Modify Constraint... menu options

The two main activities that will be performed on a newly created constraint file are specifying the part (device) and applying port constraints.

## 6.3.1 Specifying the part (device)

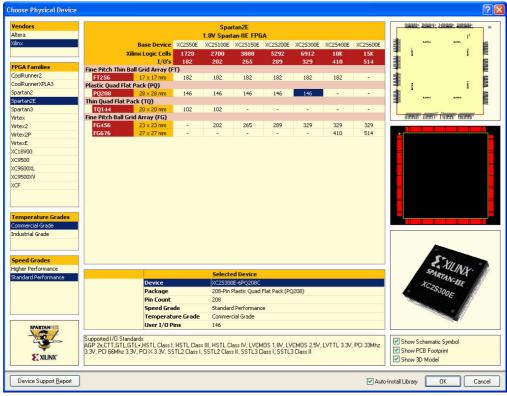

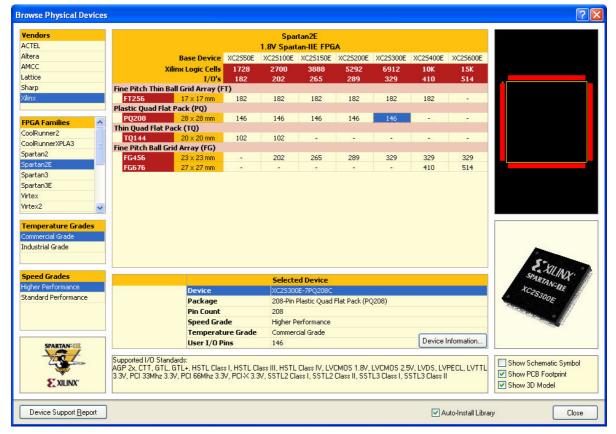

The design can be constrained to a specific device by selecting **Add/Modify Constraint » Part** and selecting the desired part from the **Choose Physical Device** dialog:

Figure 21. Choose Physical Device dialog box.

Select the Vendor, Family, Device and Temperature/Speed grades as desired and click OK. A line similar to the one below will be automatically inserted into the constraint file: **Record=Constraint | TargetKind=Part | TargetId=**XC2S300E-6PQ208C

#### 6.3.2 Specifying port constraints

Use the **Add/Modify Constraint » Port** to apply a constraint to a port in the FPGA project.

| Add/Modify Port  | Constraint     | ? 🗙    |

|------------------|----------------|--------|

| Target           | CLK_BRD        | ~      |

| Constraint Kind  | FPGA_CLOCK_PIN | ~      |

| Constraint Value | True           | ~      |

|                  | ОК             | Cancel |

Figure 22. Add/Modify Port Constraint dialog box.

Selecting OK from the dialog box in Figure 22 will cause the following constraint to be added to the constraint file:

Record=Constraint | TargetKind=Port | TargetId=CLK\_BRD | FPGA\_CLOCK\_PIN=True

This constraint will ensure that the Vendor FPGA tools route the CLK\_BRD port to a specialized clock pin on the target device.

Alternatively, the FPGA PINNUM

constraint can be specified to lock the port to a specific pin on the target device.

| Add/Modify Port  | Constraint  | ? 🔀    |

|------------------|-------------|--------|

| Target           | CLK_BRD     | ~      |

| Constraint Kind  | FPGA_PINNUM | ~      |

| Constraint Value | P185        | ~      |

|                  | ОК          | Cancel |

Figure 23. Add/Modify Port Constraint dialog box.

Selecting OK from the dialog box in Figure 23 will add the constraint **FPGA\_PINNUM**=P185 to the CLK\_BRD port constraint.

#### 6.3.3 Applying further constraints

Additional constraints other than those discussed here are available. Consult the **TR0103 Constraint File Reference.pdf** document for more information.

To summarize:

- **Constraint files** store implementation specific information such as device pin allocations and electrical properties.

- A **Configuration** is a grouping of one or more constraint files and describes how the FPGA project should be built.

### 6.4 NanoBoard constraint files

Constraint files for use with the NanoBoard daughter board modules can be found in the \Program Files\Altium Designer 6\Library\Fpga directory. To protect these system files from inadvertent modification, it is advisable to make this directory 'read only'.

## 6.5 Configurations

A *Configuration* is a set of one or more constraint files that must be used to target a design for a specific output. The migration of a design from prototype to production will often involve several PCB iterations and possibly even different FPGA devices. In this case, a separate configuration would be used to bring together constraint file information for each design iteration. Each new

configuration (and its associated constraint file(s) ) is stored with the project and can be recalled at any time.

Because configurations can contain multiple constraint files, it can sometimes be helpful to split constraint information across multiple constraint files. Usually one would separate the constraint files according to the class of information they contain:

#### 6.5.1 Device and board constraint information:

The specific FPGA device must be identified and ports defined in the top level FPGA design must be mapped to specific pin numbers.

#### 6.5.2 Device resource constraint information:

In some designs it may be advantageous to make use of vendor specific resources that are unique to a given FPGA device. Some examples are hardware multiplication units, clock multipliers and memory resources.

#### 6.5.3 Project or design constraint information:

This would include requirements which are associated with the logic of the design, as well as constrains on its timing. For example, specifying that a particular logical port must be allocated to global clock net, and must be able to run at a certain speed.

### 6.6 Configuration Manager

The grouping of multiple constraints into a single configuration is managed via the *Configuration Manager*, accessible by right-clicking the FPGA project in the Projects panel and selecting **Configuration Manager** from the menu.

| Configuration Manager For SpiritLevel.PRJFPG                                                     |              |                    |             |           |  |  |

|--------------------------------------------------------------------------------------------------|--------------|--------------------|-------------|-----------|--|--|

| Constraint Files                                                                                 |              | Configurations     |             |           |  |  |

| Constraint Filename                                                                              | NB_Cycll_240 | NB_Xilinx_Spartan2 | SpiritLevel | Target_2E |  |  |

| NB1_6_EP1C12Q240.Constraint                                                                      |              |                    |             |           |  |  |

| NB1_6_XC2S300E-6PQ208.Constraint                                                                 |              | ✓                  |             |           |  |  |

| SpiritLevel.Constraint                                                                           |              |                    | <b>v</b>    |           |  |  |

| Target_2E.Constraint                                                                             |              |                    |             | ✓         |  |  |

|                                                                                                  |              |                    |             |           |  |  |

| Configurations Add Delete Rename Constraint Files Add Remove V Force Columns Into View OK Cancel |              |                    |             |           |  |  |

Figure 24. Configuration Manager showing multiple configurations and constraint files.

Figure 24 shows the *Configuration Manager* dialog for a project that contains multiple configurations and constraint files. The Constraint files are listed in the left column and can be included in a Configuration (listed as the headings in the four right columns) by placing a tick at the row/column intersection point. Although this example only shows one constraint file being used in each of the configurations, there is no reason why a constraint file can't be used by more than one configuration nor is there any reason why a configuration can't make use of multiple constraint files.

## 6.7 Exercise 2 – Configuring MyPWM

1. Right click on the MyPWM.PRJFPG in the **Projects** panel and select *Configuration Manager* from the menu. The *Configuration Manager* should be empty as depicted in Figure 25.

| Constra            | aint Files | C | Configurations |  |

|--------------------|------------|---|----------------|--|

| onstraint Filename | 1          |   |                |  |

|                    |            |   |                |  |

|                    |            |   |                |  |

|                    |            |   |                |  |

|                    |            |   |                |  |

|                    |            |   |                |  |

|                    |            |   |                |  |

Figure 25. Configuration Manager with no Constraint Files or Configurations defined.

- 2. Because we are targeting our design for the NanoBoard, we will be using an existing constraint file that has been previously defined for the Spartan-II daughter board. Select the Add button next to the Constraint Files label. The Choose Constraint files to add to Project dialog box will be displayed. By default it should open in the Altium Designer 6\Library\FPGA directory. If it hasn't defaulted to this location then navigate to it.

- 3. Select the constraint file labelled NB1\_6\_XC2S300E-6PQ208.Constraint and click Open. You should see the same as Figure 26.

| Configuration Manager For MyPWM.PRJFPG |                                                                 |

|----------------------------------------|-----------------------------------------------------------------|

| Constraint Files                       | Configurations                                                  |

| Constraint Filename A                  |                                                                 |

| NB1_6_XC2S300E-6PQ208.Constraint       |                                                                 |

|                                        |                                                                 |

|                                        |                                                                 |

|                                        |                                                                 |

|                                        |                                                                 |

| Configurations Add Delete Rename       | Constraint Files Add Remove V Force Columns Into View DK Cancel |

Figure 26. Configuration Manager with Spartan-II daughter board constraint file present.

4. We shall now create a configuration that will make use of this constraint file. Select the **Add** button located next to the **Configurations** label.

| New Configuration      |        | × |

|------------------------|--------|---|

| New Configuration Name |        |   |

| NB_SpartanIIE          |        |   |

| ОК                     | Cancel |   |

Figure 27. Specifying a new configuration.

- 5. Call the new configuration NB\_SpartanIIE and select OK.

- 6. Click on the checkbox to link the NB1\_6\_XC2S300E-6PQ208.Constraint file to the NB\_SpartanIIE configuration.

| Configuration Manager For MyPWM.PRJFPG |                                                                     |

|----------------------------------------|---------------------------------------------------------------------|

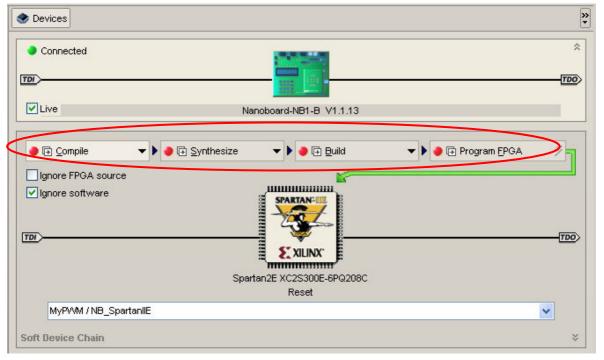

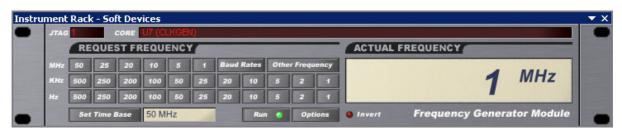

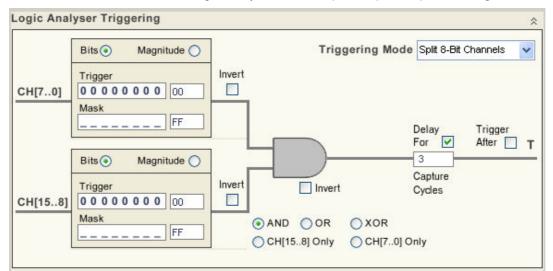

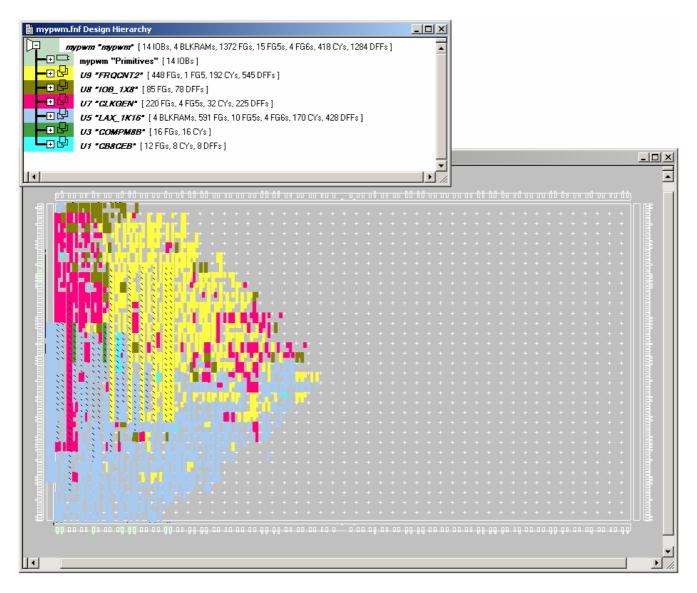

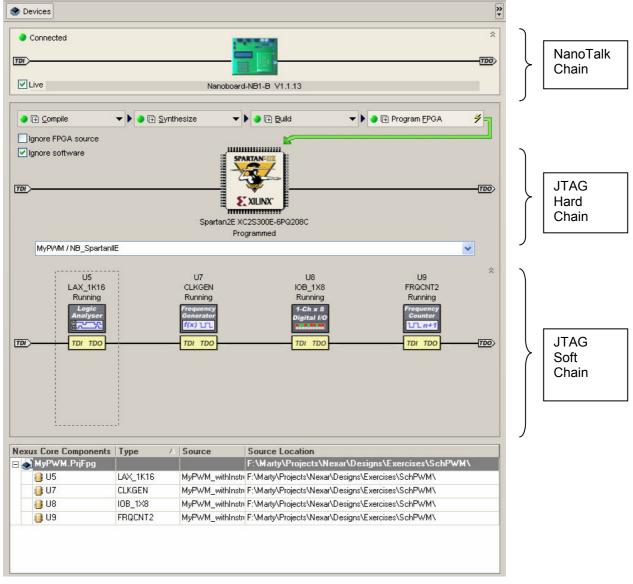

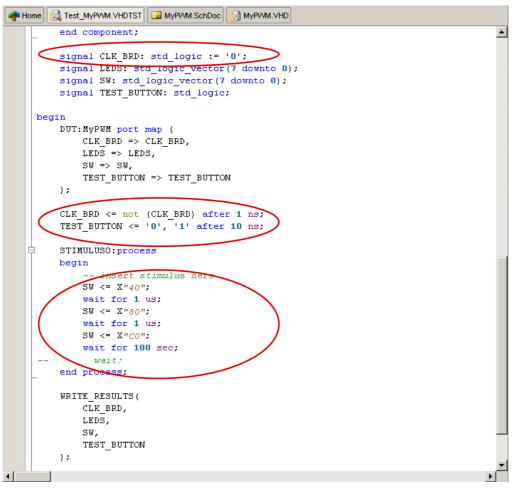

| Constraint Files                       | Configurations                                                      |