# AVR-Grundlagen Teil 2

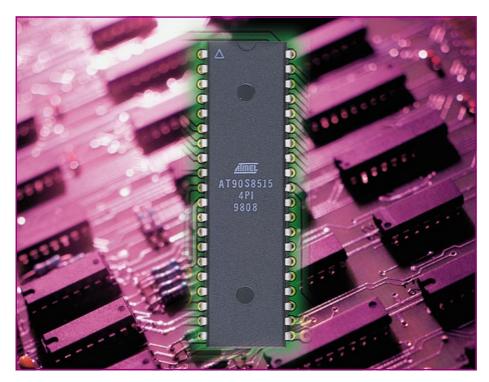

Die AVR-Mikrocontroller erfreuen sich stetig wachsender Beliebtheit unter Schaltungsentwicklern sowohl im professionellen als auch im privaten Bereich. Sie zeichnen sich durch eine hohe Verarbeitungsgeschwindigkeit und eine Vielzahl verschiedener Typen aus, sodass man quasi zu jedem Projekt über den passenden Controller verfügen kann. In dieser Artikelserie wird die Controller-Baureihe vorgestellt und anhand von Anwendungsbeispielen erläutert. Nachdem wir im ersten Teil den Aufbau und die grundlegende Beschaltung der Controller besprochen haben, erfolgt nun die Beschreibung des Befehlssatzes, die Vorstellung der Register mit ihren speziellen Funktionen, z. B. zur Timersteuerung, dem Zugriff auf das interne EEPROM usw. Schließlich beschreiben wir den Grundaufbau eines Programms im AVR-Assembler.

#### **Der Befehlssatz**

Der Befehlssatz der AVR-Mikrocontroller umfasst 89 bis 128 Befehle, abhängig vom verwendeten Controllertyp. Welche Befehle für den einzelnen Mikrocontroller verfügbar sind, entnimmt man dem jeweiligen Datenblatt, das unter [1] verfügbar ist. Um sich einen ersten Überblick zu verschaffen, sind die Befehle in Gruppen aufgeteilt: arithmetische und logische Befehle, Bit- und Bit-Test-Funktionen, Datentransfer und Sprungbefehle.

Bevor wir tiefer in den Befehlssatz einsteigen, müssen die notwendigen Register und Operanden betrachtet werden.

#### Register

Der Registerbereich umfasst 32 Register zu je 8 Bit, welche über die Bezeichner "R0" bis "R31" ansprechbar sind.

Neben der Registerbank gibt es den Bereich des Datenspeichers, den man über zwei verschiedene Arten adressieren kann. Bei der direkten Adressierung wird die Speicherstelle unmittelbar über die Adresse oder den zugehörigen Bezeichner angesprochen, d. h. der Zahlenwert der Adresse wird als Operand des entsprechenden Befehls angegeben. Andere Befehle unterstützen die indirekte Adressierung, d. h., dass auf Daten im SRAM nicht über die konstante Adresse, die fest im Programm

verankert ist, zugegriffen wird, sondern die Speicheradresse wird während der Laufzeit in einem bestimmten Bereich der Registerbank abgespeichert und vom Befehl als Adresse interpretiert. Eine solche Registerbankvariable bezeichnet man auch als "Zeiger", da der enthaltene Wert auf einen Bereich im Speicher zeigt. Diese Zeiger sind beim AVR-Assembler mit X, Y und Z deklariert und aus jeweils zwei Registern zusammengesetzt (X=R27:R26, Y=R29:R28, Z=R31:R30). Sie haben eine Breite von 16 Bit und können somit einen Speicherbereich von bis zu 64 KB adressieren.

Ein weiteres Register ist das Statusregister, welches die wichtigsten Flags enthält.

#### **Flags**

Ein Flag (Flagge) ist ein Bit, das das Auftreten bestimmter Ereignisse oder Zustände kenntlich macht und nur die Werte Null oder Eins annehmen kann.

Das Carry-Flag wird immer dann gesetzt, wenn es einen Überlauf bei einer Operation gegeben hat. Addiert man mit 8 Bit breiten Registern (max. Zahlenwert 255) die Werte 230 und 56, dann gibt es einen Überlauf, da das Zielregister den Zahlenwert von 286 nicht aufnehmen kann. Stattdessen wird das "Carry-Flag" (C) zur Erkennung des Überlaufs in die nächsthöhere Stelle, welche einen Wert von 256 hat, gesetzt. Das Zielregister enthält danach den Wert 30. Es geht keine Information verloren.

Ein weiteres wichtiges Flag ist das "Zero-Flag" (Z). Es wird gesetzt, wenn das Ergebnis einer mathematischen Operation gleich Null ist. Ein gesetztes Zero-Flag nach einer Subtraktion bedeutet, dass die beiden Operanden den gleichen Wert hatten

Das "Negativ-Flag" (N) kennzeichnet ein negatives Ergebnis, falls man vorzeichenbehaftete Operationen durchführt. Ansonstenist das Negativ-Flag immer identisch mit der höchstwertigsten Stelle des Ergebnisses.

#### Befehlsübersichten

Eine Übersicht über diese und weitere Flags befindet sich in Tabelle 1, ebenso wie die in der Befehlsbeschreibung verwendeten Abkürzungen.

Die Tabellen 2 bis 5 enthalten eine Kurzübersicht aller von den AVR-Mikrocontrollern unterstützten Befehle. Eine ausführliche Beschreibung findet man unter [2] auf der Atmel-Homepage.

In diesen Tabellen gibt es jeweils drei Spalten mit den wichtigsten Informationen. Die erste Spalte zeigt den Befehl, in der zweiten stehen die notwendigen Operanden, gefolgt von der Kurzbeschreibung.

16 ELVjournal 5/01

|                         | Tabelle 1: Bezeichner zur Beschreibung des Befehlssatzes |        |                                      |  |  |  |  |  |  |  |

|-------------------------|----------------------------------------------------------|--------|--------------------------------------|--|--|--|--|--|--|--|

| Statusregister (SREG) F |                                                          |        | Register und Operanden               |  |  |  |  |  |  |  |

| SREG:                   | Statusregister                                           | Rd:    | Ziel- und Quellregister              |  |  |  |  |  |  |  |

| C:                      | Carry-Flag                                               | Rr:    | Quellregister                        |  |  |  |  |  |  |  |

| Z:                      | Zero Flag                                                | R:     | Ergebnis nach Befehls-               |  |  |  |  |  |  |  |

| N:                      | Negative-Flag                                            |        | ausführung                           |  |  |  |  |  |  |  |

| V:                      | Flag zur Erkennung eines                                 | K:     | Konstante Daten                      |  |  |  |  |  |  |  |

|                         | Überlaufs beim                                           | k:     | Konstante Adresse                    |  |  |  |  |  |  |  |

|                         | Zweier-Komplement                                        |        | (Direkte Adressierung)               |  |  |  |  |  |  |  |

| S:                      | Sign-Flag (Vorzeichen)                                   | b:     | Bit in Registerbank oder im          |  |  |  |  |  |  |  |

|                         |                                                          |        | I/O-Bereich                          |  |  |  |  |  |  |  |

| H:                      | Half-Carry-Flag                                          | s:     | Bit im Statusregister                |  |  |  |  |  |  |  |

| T:                      | Transfer-Bit                                             | X,Y,Z: | Register zur indirekten Adressierung |  |  |  |  |  |  |  |

|                         | (wird von BLD- und                                       |        |                                      |  |  |  |  |  |  |  |

|                         | BST-Befehlen verwendet)                                  |        |                                      |  |  |  |  |  |  |  |

|                         |                                                          | A:     | I/O-Adresse                          |  |  |  |  |  |  |  |

|                         |                                                          | PC:    | Befehlszähler                        |  |  |  |  |  |  |  |

| I:                      | Globales Interrupt-Enable-Fl                             | ag     |                                      |  |  |  |  |  |  |  |

In der nächsten Spalte sind alle Flags aufgeführt, die von diesem Befehl beeinflusst werden. Abschließend findet man noch die benötigten Taktzyklen, die zur Ausführung der Funktion notwendig sind.

Tabelle 2 zeigt die Arithmetik- und Logikbefehle, mit denen mathematische Funktionen realisierbar sind. Zu den Grundfunktionen gehören hier die Addition, die Subtraktion sowie die Multiplikation zwischen zwei Registern oder einem Register und einer Konstanten. Des Weiteren sind Befehle zum gezielten Verändern eines

Registers enthalten (Inkrementieren, Dekrementieren, Löschen, Setzen usw.). Andere mathematische Funktionen (z. B. Division) lassen sich durch kleine Routinen mit den vorhandenen Befehlen einfach realisieren.

Um die in einem Programmablauf notwendigen Verzweigungen ausführen zu können, verfügen die AVR-Mikrocontroller über vielfältige Sprunganweisungen, wie man sie in Tabelle 3 zusammengefasst findet.

Am Anfang der Tabelle befinden sich

die Sprunganweisungen, die beim Aufruf an die angegebene Adresse im Programmspeicher springen (RJMP, IJMP, EIJMP, JMP). Anschließend sind die Befehle zur Behandlung von Unterfunktionen (Subroutine) und Interrupt-Service-Routinen angegeben. Ein Funktionsaufruf erfolgt über einen "CALL"-Befehl (RCALL, ICALL, EICALL, CALL). Da bei einem solchen Befehl die spätere Rücksprungadresse im Stack gespeichert wird, muss der Rücksprung zur aufrufenden Routine mit dem "RET"-Befehl erfolgen, der die Adresse wieder aus dem Stack holt und damit das Programm an der korrekten Stelle fortführt.

Interrupt-Service-Routinen, die beim Auftreten einer Unterbrechungsanforderung automatisch aufgerufen werden, müssen mit dem "RETI"-Befehl verlassen werden, da der Aufruf und Rücksprung andere Prozessoraktionen als bei einer normalen Unterroutine auslöst.

Die bisher noch nicht besprochenen Befehle dienen zur Ausführung bedingter Verzweigungen. Der Befehl "CPSE" vergleicht die beiden Operanden und überspringt den folgenden Befehl, falls der Inhalt dieser Register gleich ist. Alle weiteren Befehle für Vergleiche (CP, CPC, CPI) führen keinen direkten Sprung aus, falls bestimmte

| Tabelle 2: Arithmetik- und Logikbefehle                        |                                                                                                           |                                                                                                                                                                                                                                               | Tabelle 3: Sprung-Anweisungen                                                                    |                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Mnemonics ADD ADC ADIW SUB SUBI SBC SBCI SBCI SBIW AND ANDI OR | Operands Rd, Rr Rd, Rr Rd, K Rd, Rr Rd, K Rd, Rr Rd, K Rd, Rr Rd, K Rd, K Rd, K Rd, K Rd, Rr Rd, K Rd, Rr | Description Add without Carry Add with Carry Add Immediate to Word Subtract without Carry Subtract Immediate Subtract with Carry Subtract Immediate with Carry Subtract Immediate from Word Logical AND Logical AND with Immediate Logical OR | Mnemonics RJMP IJMP EIJMP JMP RCALL ICALL EICALL CALL RET RETI CPSE                              | Operands<br>k<br>k<br>k<br>k                                                       | Description Relative Jump Indirect Jump to (Z) Extended Indirect Jump to (Z) . Jump Relative Call Subroutine Indirect Call to (Z) Extended Indirect Call to (Z) Call Subroutine Subroutine Return Interrupt Return Compare, Skip if Equal                                                                                                                                                                 |  |

| ORI EOR COM NEG SBR CBR INC DEC TST CLR SER MUL                | Rd, K<br>Rd, Rr<br>Rd<br>Rd, K<br>Rd, K<br>Rd<br>Rd<br>Rd<br>Rd<br>Rd<br>Rd<br>Rd, Rr                     | Logical OR with Immediate Exclusive OR One's Complement Two's Complement Set Bit(s) in Register Clear Bit(s) in Register Increment Decrement Test for Zero or Minus Clear Register Set Register Multiply Unsigned                             | CP<br>CPC<br>CPI<br>SBRC<br>SBRS<br>SBIC<br>SBIS<br>BRBS<br>BRBC<br>BRBC<br>BREQ<br>BRNE<br>BRCS | Rd,Rr<br>Rd,Rr<br>Rd,K<br>Rr, b<br>Rr, b<br>A, b<br>A, b<br>s, k<br>s, k<br>k<br>k | Compare Compare with Carry Compare with Immediate Skip if Bit in Register Cleared Skip if Bit in I/O Register Cleared Skip if Bit in I/O Register Cleared Skip if Bit in I/O Register Set Branch if Status Flag Set Branch if Status Flag Cleared Branch if Equal Branch if Not Equal Branch if Carry Set                                                                                                 |  |

| MULS<br>MULSU<br>FMUL<br>FMULS<br>FMULSU                       | Rd,Rr<br>Rd,Rr<br>Rd,Rr<br>Rd,Rr<br>Rd,Rr<br>Rd,Rr                                                        | Multiply Signed Multiply Signed with Unsigned Fractional Multiply Unsigned Fractional Multiply Signed Fractional Multiply Signed with Unsigned                                                                                                | BRCC BRSH BRLO BRMI BRPL BRGE BRLT BRHS BRHC BRTS BRTC BRVS BRVC BRIE                            | k<br>k<br>k<br>k<br>k<br>k<br>k<br>k                                               | Branch if Carry Cleared Branch if Same or Higher Branch if Lower Branch if Minus Branch if Plus Branch if Greater or Equal, Signed Branch if Less Than, Signed Branch if Half Carry Flag Set Branch if Half Carry Flag Cleared Branch if T Flag Set Branch if T Flag Set Branch if Overflow Flag is Set Branch if Overflow Flag is Cleared Branch if Overflow Flag is Cleared Branch if Interrupt Enabled |  |

ELVjournal 5/01

| Tabelle 4: Befehle zum Datentransfer |             |                                                    | Tabelle 5: Bit- und Bit-Test-Befehle              |                                |                                 |  |

|--------------------------------------|-------------|----------------------------------------------------|---------------------------------------------------|--------------------------------|---------------------------------|--|

| Mnemonics Operands Description       |             |                                                    | Mnemonic                                          | Mnemonics Operands Description |                                 |  |

| MOV                                  | Rd, Rr      | Copy Register                                      | LSL                                               | Rd                             | Logical Shift Left              |  |

| MOVW                                 | Rd, Rr      | Copy Register Pair                                 | LSR                                               | Rd                             | Logical Shift Right             |  |

| LDI                                  | Rd, K       | Load Immediate                                     | ROL                                               | Rd                             | Rotate Left Through Carry       |  |

| LDS                                  | Rd, k       | Load Direct from data space                        | ROR                                               | Rd                             | Rotate Right Through Carry      |  |

| LD                                   | Rd, X       | Load Indirect                                      | ASR                                               | Rd                             | Arithmetic Shift Right          |  |

| LD                                   | Rd, X+      | Load Indirect and Post-Increment                   | SWAP                                              | Rd                             | Swap Nibbles                    |  |

| LD                                   | Rd, -X      | Load Indirect and Pre-Decrement                    | BSET                                              | S                              | Flag Set                        |  |

| LD                                   | Rd, Y       | Load Indirect                                      | BCLR                                              | S                              | Flag Clear                      |  |

| LD                                   | Rd, Y+      | Load Indirect and Post-Increment                   | SBI                                               | A, b                           | Set Bit in I/O Register         |  |

| LD                                   | Rd, -Y      | Load Indirect and Pre-Decrement                    | CBI                                               | A, b                           | Clear Bit in I/O Register       |  |

| LDD                                  | Rd,Y+q      | Load Indirect with Displacement                    | BST                                               | Rr, b                          | Bit Store from Register to T    |  |

| LD                                   | Rd, Z       | Load Indirect                                      | BLD                                               | Rd, b                          | Bit load from T to Register     |  |

| LD                                   | Rd, Z+      | Load Indirect and Post-Increment                   | SEC                                               |                                | Set Carry                       |  |

| LD                                   | Rd, -Z      | Load Indirect and Pre-Decrement                    | CLC                                               |                                | Clear Carry                     |  |

| LDD                                  | Rd, Z+q     | Load Indirect with Displacement                    | SEN                                               |                                | Set Negative Flag               |  |

| STS                                  | k, Rr       | Store Direct to data space                         | CLN                                               |                                | Clear Negative Flag             |  |

| ST                                   | X, Rr       | Store Indirect                                     | SEZ                                               |                                | Set Zero Flag                   |  |

| ST                                   | X+, Rr      | Store Indirect and Post-Increment                  | CLZ                                               |                                | Clear Zero Flag                 |  |

| ST                                   | -X, Rr      | Store Indirect and Pre-Decrement                   | SEI                                               |                                | Global Interrupt Enable         |  |

| ST                                   | Y, Rr       | Store Indirect                                     | CLI                                               |                                | Global Interrupt Disable        |  |

| ST                                   | Y+, Rr      | Store Indirect and Post-Increment                  | SES                                               |                                | Set Signed Test Flag            |  |

| ST                                   | -Y, Rr      | Store Indirect and Pre-Decrement                   | CLS                                               |                                | Clear Signed Test Flag          |  |

| STD                                  | Y+q,Rr      | Store Indirect with Displacement                   | SEV                                               |                                | Set Two's Complement Overflow   |  |

| ST                                   | Z, Rr       | Store Indirect                                     | CLV                                               |                                | Clear Two's Complement Overflow |  |

| ST                                   | Z+, Rr      | Store Indirect and Post-Increment                  | SET                                               |                                | Set T in SREG                   |  |

| ST                                   | -Z, Rr      | Store Indirect and Pre-Decrement                   | CLT                                               |                                | Clear T in SREG                 |  |

| STD                                  | Z+q,Rr      | Store Indirect with Displacement                   | SEH                                               |                                | Set Half Carry Flag in SREG     |  |

| LPM                                  | 5.7         | Load Program Memory                                | CLH                                               |                                | Clear Half Carry Flag in SREG   |  |

| LPM                                  | Rd, Z       | Load Program Memory                                | NOP                                               |                                | No Operation                    |  |

| LPM                                  | Rd, Z+      | Load Program Memory and Post-                      | SLEEP                                             |                                | Sleep                           |  |

| EL DM                                |             | Increment                                          | WDR                                               |                                | Watchdog Reset                  |  |

| ELPM                                 | D-1 -7      | Extended Load Program Memory                       |                                                   |                                |                                 |  |

| ELPM                                 | Rd, Z       | Extended Load Program Memory                       |                                                   |                                | Internet:                       |  |

| ELPM                                 | Rd, Z+      | Extended Load Program Memory                       | [ [1] D / 1                                       | 1                              |                                 |  |

| CDM                                  |             | and Post-Increment                                 | [1] Datenbl                                       |                                |                                 |  |

| SPM<br>ESPM                          |             | Store Program Memory                               | http://www                                        | atmel.com/at/                  | mel/products/prod200.htm        |  |

|                                      | Dd A        | Extended Store Program Memory In From I/O Location |                                                   |                                |                                 |  |

| IN<br>OUT                            | Rd, A       | Out To I/O Location                                | [2] Befehlssatz der AVR-Controller im PDF-Format: |                                |                                 |  |

| PUSH                                 | A, Rr<br>Rr | Push Register on Stack                             | http://www.atmel.com/atmel/acrobat/doc0856.pdf    |                                |                                 |  |

| POP                                  | Rd<br>Rd    | Pop Register from Stack                            | nup.//www                                         | .aumen.com/at                  | men acrouat doctosso.pur        |  |

| 1 OF                                 | ilu         | 1 op negister nom stack                            |                                                   |                                |                                 |  |

Bedingungen erfüllt sind, sondern führen intern nur eine Subtraktion durch, welche die Flags im Statusregister entsprechend setzt oder zurücksetzt. Ein nachfolgender Befehl zum Verzweigen (BRBS, BRBC, BREQ usw.) wertet diese Flags aus und führt bei positivem Ergebnis den Sprung an die angegebene Stelle des Programms

Die meisten Befehle der AVR-Controller arbeiten nur mit der Registerbank und können nicht direkt auf den Datenspeicher zugreifen. Deshalb ist es notwendig, die Daten aus dem Datenspeicher im SRAM auf die Registerbank zu übertragen, sodass die entsprechenden Operationen durchgeführt werden können. In Tabelle 4 sind die Befehle zum Datentransfer zusammengefasst.

Der abschließende Teil der Befehle ist in Tabelle 5 zu sehen. Alle aufgeführten Anweisungen dienen zum Manipulieren oder zum Testen einzelner Bits.

## Special-Function-Register (SFR)

Neben den 32 Arbeitsregistern der Registerbank, die für allgemeine Programmabläufe nutzbar sind, gibt es auch die so

genannten "Special-Function-Register" oder kurz "SFR", denen, wie der Name schon sagt, spezielle Funktionen zugewiesen sind. Über diese SFR erfolgt die Steuerung und der Betrieb der im Mikrocontroller integrierten Peripherie (Timer/Counter, EEPROM, UART usw.). Diese Register sind also eng mit der Hardware verbunden und können somit zwischen den einzelnen Controllertypen variieren. Die genauen Eigenschaften und Bedeutungen der einzelnen Register zum passenden Mikrocontroller sind in den entsprechenden Datenblättern [2] aufgeführt.

### Der Programmaufbau

Jeder AVR-Mikrocontrollertyp hat unterschiedliche Speichergrenzwerte, SFR usw., die in einer Datei zusammengefasst sind. In diesen Include-Dateien werden die in den Datenblättern angegebenen Bezeichnungen der Register und Bits mit den entsprechenden Adressen verknüpft. Zu Beginn eines jeden Programmes muss deshalb die controllerspezifische Datei eingebunden werden.

Das Programm startet nach einem Reset

immer an der Adresse 0 im Programmspeicher, sodass dort die entsprechende Verzweigung zum eigentlichen Programmstart erfolgen muss.

Auf eine Unterbrechungsanforderung (Interrupt) erfolgt, bei eingeschaltetem Interrupt, der automatische Sprung an die festgelegte Adresse im Programmspeicher. Die Einsprungadressen der verschiedenen Interruptquellen starten im Programmspeicher ab 1. Das bedeutet, dass an diesen Stellen jeweils Verzweigungen zu den entsprechenden Interrupt-Service-Routinen erfolgen müssen, in denen die Bearbeitung der Unterbrechungsanforderung erfolgt.

Das Programm sollte nach einem Reset immer mit der Initialisierung der Special-Function-Register sowie der Variablen beginnen, damit das nachfolgende Programm beim Start immer die richtigen Bedingungen vorfindet.

Damit ist der zweite Teil der Artikelserie "AVR-Grundlagen" abgeschlossen. Im nächsten "ELVjournal" wird ein erstes Projekt anhand eines kleinen Beispielprogrammes implementiert, wobei wir die Entwicklungsumgebung für diese Mikrocontroller, das "AVR-Studio", nutzen.

18 ELVjournal 5/01